STM32 时钟树概念及配置思路

我们为什么需要时钟?

在一般芯片电路中,光信号的传播速度非常快,可以不计入时间,而电信号如果经过了芯片或者门电路,就会遇到延迟,如果这个延时不能很好的校对清楚,那么就会出现在二者时间差内产生奇怪的输出信号

因此我们在每一个输入到芯片的电路中添加一个时间管理器,即按照一定周期输出方波,芯片内部捕获上升沿,也就是说只有在电路信号在时钟达到上升沿的时候才会将信号传入处理器内部

同时,不同的外设装置例如串口,I2C总线等都有自己的时钟来判断是否要继续发送,这些时钟也需要被统一管理,因此我们需要一个时钟树来管理这些时钟

先进高性能总线 Advanced High-performance Bus AHB

这是 STM32 的内部总线,主要用于连接 CPU 和内部存储器,以及连接外设总线,其时钟线称为 HCLK

HCLK 与 cpu、内存、dma 的时间总线直接相连,因此频率相等

在处理器内部会存在一个 SystemTick 计时器用来给程序提供时间基准,一般是 72 MHz

分频器

一般是对频率做除法,比如我们将 HCLK 分频为 1/2,那么我们就可以得到 HCLK/2 的频率

SystemTick 计时器到总线的分频器是 /8

先进外设总线 Advanced Peripheral Bus APB

在 STM32 中,I2C,SPI,USART 等外设都是通过 APB 总线连接到 CPU 的,APB 也有自己的时钟线,称为 PCLK1 和 PCLK2

APB 会桥接到 AHB 总线上,他们之间会存在:

- 分频器用于降低 AHB 总线上面的频率

- 倍频器 专门给 APB 上面的通用定时器,如果 分频器为/1 那么 倍频器的值为 x1; 如果 分频器为 /2/4/8/16 那么 倍频器的值为 x2 (这在cubeMX 中是不可以自己设置的)

- 定时器和外设总线在两条支路上,二者互不干扰

系统时钟源

HCLK 的时钟来自两个,分别为 HSI 和 HSE:

- 高速内部时钟

HSI(也称为内部RC振荡器,或HSI)的默认频率为16 MHz - 高速外部时钟源

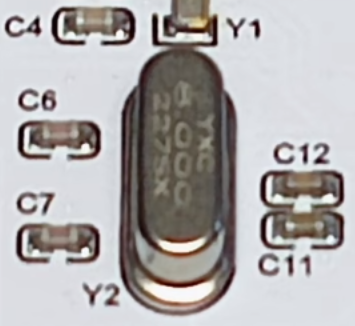

HSE在本板子上为8 MHz一般需要外接一个晶振 (长得如下)

-

但是聪明的你一定发现了,这里的时钟信号是小于 72 MHz (HCLK 主要频率)的,那么我们怎么以小搏大呢?

我们在两种时钟源连接 HCLK 之前会先通过分频器连接到 PLL 锁相环(当然一般用哪个连哪个),这个锁相环会将时钟源的频率倍频,范围 x2 - x16,然后输出到 一个叫 SystemCLK 的时钟线上,这个时钟线通过一个分频器连接到 HCLK 上

自由时钟总线 FCLK

这个时钟频率和 HCLK 一致,但是并不来自 HCLK, 它来自 SystemCLK 通过一个分频器连接到 FCLK 上

这个分频器的作用是 在系统休眠,HCLK 停止工作的时候时刻准备唤醒 HCLK

慢速时钟源 LSI, LSE

一般的 iwdg 看门狗会使用这个时钟源

All articles in this blog are licensed under CC BY-NC-SA 4.0 unless stating additionally.