1. 指令集架构 Instruction Set Architecture, ISA

ISA 可以看作是连接汇编层代码和硬件的操控指令集合, 例如 汇编会有 ADD r1, r2, r3 的指令,我们利用 ISA 就会将指令转换为 r2 + r3 -> r1

常见分类 Classification

x86 架构

由 intel 公司开发,为 32 位处理器,一般在上世纪末的电脑中比较常见

由于 即地址循迹的范围小于等于 4GB, 也就是内存大小不超过 4G

amd64 架构

由 amd 公司在上世纪发明,一般为 64 位处理器,后面 intel 公司也制造这个架构

现在被大量的 pc 使用

ARM 板 Advanced RISC Machine

设计公司是 arm, 非常适用于移动通信领域, 具有 低成本、高性能、低耗电的特性

现在用于大量的手机等可移动设备使用

近年来的 mac silicone 用 arm 架构

RISC-V 锐克五代

- 开源

- 学术界青睐,因为没有昂贵的 license 费用

硬件发展与运算速度

Moore’s Law

由 Intel 创始人之一戈登·摩尔提出

集成电路上可容纳的晶体管数目,约每隔两年便会增加一倍

Dennard Scaling

随着晶体管变小,其功率密度保持不变,因此功耗与面积成比例

局限性

自 2005-2007 年左右以来,登纳德缩放定律似乎已失效。截至 2016 年,集成电路中的晶体管数量仍在增长,但由此带来的性能提升比频率大幅提高带来的加速更为缓慢。

失效的主要原因是,在小尺寸下,电流泄漏会带来更大的挑战,还会导致芯片发热,从而造成热失控的威胁,从而进一步增加能源成本

内存的问题 Memory

计算机运行程序的时候,其实会将程序保存在一定的数字地址中。

在计算机中,数值按照二进制进行保存,因为计算机使用的线只能读取到高低电平,即 0-1 分布

二进制的优化

由于二进制数太长且不适合人类阅读,我们用 2 的指数倍作为进制基底来快速化简二进制,所以诞生了 16 进制 (hexadecimal) 在书写的时候:

- 二进制的写法: 0b 开头 + 剩余内容

- 十六进制的写法: 0x 开头 + 剩余内容

内存与寄存器

C 语言指令是操作变量的,而汇编语言是操作地址的,这会导致指令非常长(地址本身很长)且内存本身的读取、存储非常慢 (对于同一块代码块,我们并不想要多次出入这块内存,因为会导致时间的严重浪费)

寄存器 register

现代的 isa 中一般会有 固定长度的硬件组成的 寄存器

对于一般的 load-store architecture:

- load: 将数值从 内存 转移到 寄存器

- store: 将数据从寄存器转移到 内存

这样,我们就不需要每次使用数据都到 内存块中去读取数据,而是可以使用寄存器直接暂存数据 (可能会涉及多个 寄存器之间的数据转存、数据运算)

指令控制流 Control Flow

在程序运行的时候,C 会不断执行下一行代码,直到 function 调用 / return / if / for / while 循环 才结束标准顺序执行

而对于一个汇编代码,会有一个程序计数器 Program Counter (PC) 来记录指令的序号,并且一直向下执行,直到:

- 遇到 branch / jump 指令

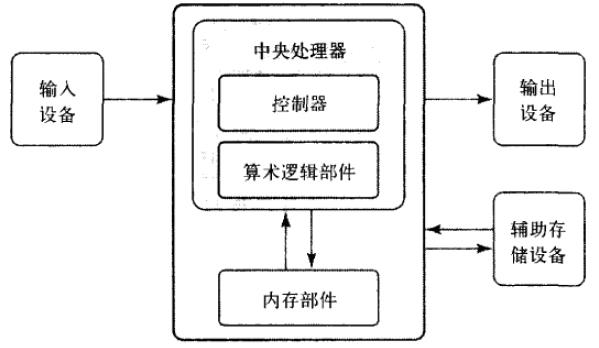

冯诺依曼架构 Von Neumann Architecture

冯诺依曼结构是什么

核心思想是将程序和数据存储在同一个存储器中,并由中央处理器(CPU)来执行

如下就是冯诺依曼的结构图

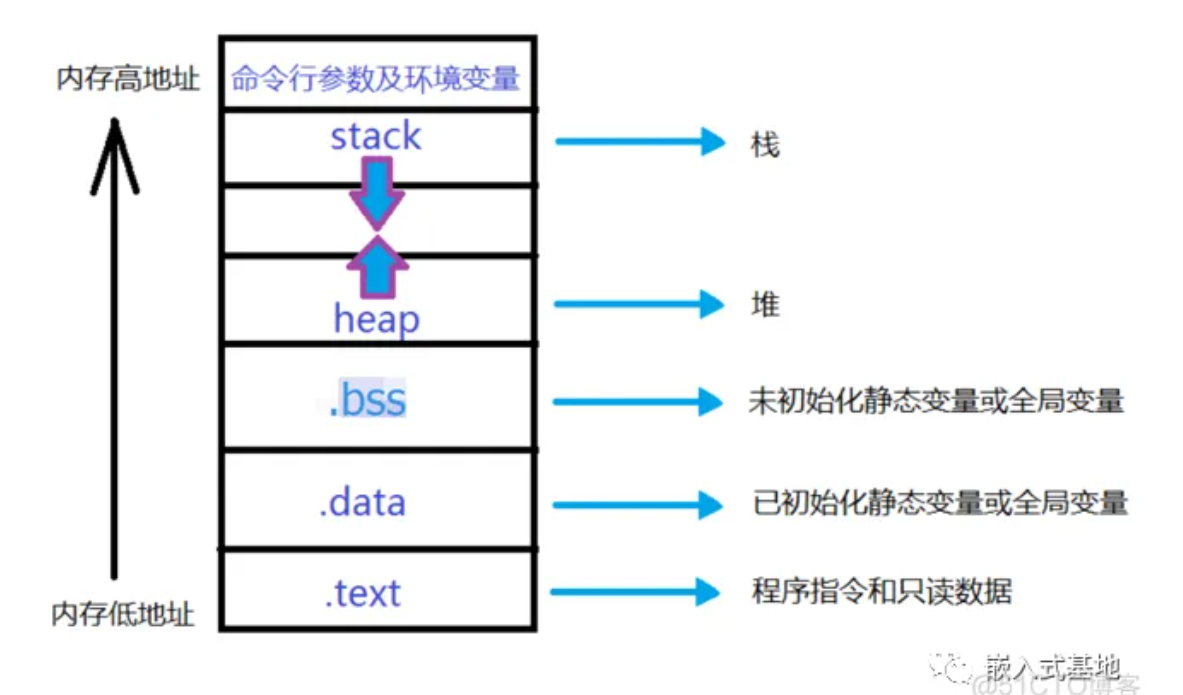

而一般的程序内存分配如下:

这个分配方式是符合冯诺依曼结构的

冯氏结构的执行逻辑

在冯诺依曼架构下,硬件会一直执行以下逻辑 (fde)

- fetch: 读取下一个指令,使用 PC 计数器找到下一个指令的内存地址 并且将之放到 指令寄存器 Instruction Register (IR)

- decode: 检查 ir 中的指令并且判断接下来要做完成什么指令

- execute: 将解码结果按照其指令执行,完成算术或者逻辑指令; 找到指令指向的地址; 更改 PC 的值 (实现循环)